|

|

|

|

Помощь Помощь

Поиск Поиск

Участники Участники

Календарь Календарь

Новости Новости

|

Учебные Материалы Учебные Материалы

ВАЛтест ВАЛтест

Фотогалерея Фотогалерея

|

Правила форума Правила форума

Виртуальные тренажеры Виртуальные тренажеры

Мемуары Мемуары

|

| Здравствуйте Гость ( Вход | Регистрация ) | Выслать повторно письмо для активации |

|

| VAL |

Дата 4.10.2019 09:08

|

Offline Мэтр, проФАН любви... proFAN of love      Профиль Группа: Администраторы Сообщений: 38172 Пользователь №: 1 Регистрация: 6.03.2004 |

(2018) Лапшинский В.А. Микросхемы "умной" ассоциативной памяти: тенденции развития, классификацияЮ применение" (статья)

SMART ASSOSIATIVE MEMORY CHIPS: TRENDS, CLASSIFICATION AND APPLICATIONS Источники: - ж. Датчики и системы, 2018, №2, с. 60-65 - http://www.datsys.ru/MAIN/Arx_D&S/2018/num_2_2018.htm - https://elib.pstu.ru/vufind/EdsRecord/edselr,edselr.32698397 Аннотация: Рассмотрены состояние, тенденции развития и области применения “умных” интегральных схем АЗУ на основе инновационной элементной базы и технологий. Приведена классификация интегральных микро- и наносхем АЗУ. Отмечено, что современная и ожидаемая степень интеграции позволяет повышать интеллектуальность таких интегральных схем. The state, development trends and application areas of “smart” associative memory chips based on the emerging element base and technologies are considered. The classification of micro- and nanoassociative memory chips is given. Noted that the modern and expected degree of integration allows increasing the intellectuality of such integrated circuits. Abstract: The state, development trends and application areas of "smart" associative memory chips based on the emerging ele-ment base and technologies are considered. The classification of micro- and nanoasso-ciative memory chips is given. Noted that the modern and expected degree of inte-gration allows increasing the intellectuality of such integrated circuits. Ключевые слова: "умные" интегральные микро- и наносхемы ассоциативной памяти, бинарные и троичные схемы памяти с адресацией по содержимому, smart micro- and nanoassociative memory chips, content addressable binary and ternary memory (BCAM and TCAM) chips. Keyword: smart micro- and nanoassociative memory chips, content addressable binary and ternary memory (BCAM and TCAM) chips. -------------------- |

| VAL |

Дата 4.10.2019 09:54

|

Offline Мэтр, проФАН любви... proFAN of love      Профиль Группа: Администраторы Сообщений: 38172 Пользователь №: 1 Регистрация: 6.03.2004 |

ВВЕДЕНИЕ

Традиционные интегральные микросхемы (ИМС) статических и динамических ОЗУ (SRAM/DRAM) основаны на хранении и выборке данных по уникальному адресу. До-полнительная процессорная логика, появляющаяся по мере роста степени интеграции, позволяет повысить их интеллектуальность [1-3]. И, тем самым, повысить эффективность применения в качестве основных ЗУ различных вычислительных систем. С другой сто-роны, для различных специализированных (пока!) применений давно известны ассоциа-тивные запоминающие устройства (АЗУ) с выборкой и обработкой данных по содержи-мому [4-9]. Сегодня уже существуют [10-13] и бурно развиваются исследования и разра-ботки в области ИМС и ИНС (интегральных наносхем) АЗУ [14-25]. По степени интегра-ции такие схемы пока отстают примерно на порядок. Хотя специалисты ожидают, что в будущем их степень интеграции достигнет уровня 1010 элементов/см2 [14]. При этом ин-теллектуальность ИНС АЗУ тоже может быть повышена с помощью дополнительной ло-гики, которая прозрачна либо видима для программного обеспечения. Настоящая статья посвящена классификации, обзору тенденций развития и примене-ния ИМС/ИНС АЗУ. В частности, «умных» схем данного типа. Следует отметить, что в сегодня в открытой отечественной литературе опубликовано довольно мало обзоров [13] и оригинальных работ в области ИМС/ИНС АЗУ, в отличие от современных зарубежных источников, число которых исчисляется десятками. -------------------- |

| VAL |

Дата 4.10.2019 09:55

|

Offline Мэтр, проФАН любви... proFAN of love      Профиль Группа: Администраторы Сообщений: 38172 Пользователь №: 1 Регистрация: 6.03.2004 |

ТЕНДЕНЦИИ И НАПРАВЛЕНИЯ РАЗВИТИЯ ИМС АЗУ

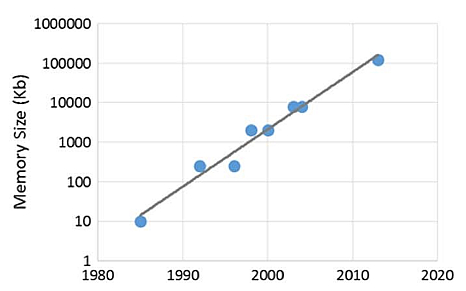

Во-первых, следует отметить, что за последние десятилетия существенно возросла и продолжает расти степень интеграции и, соответственно, информационная емкость инте-гральных схем АЗУ [10, 14], рис. 1. Этот рост при построении и реализации ИМС/ИНС АЗУ обусловлен как масштабированием традиционной КМОП технологии, так и приме-нением инновационных технологий [14-25]. Например, энергонезависимой памяти с вы-сокой степенью интеграции [24, 25], рис. 2. Разнообразие и постоянное расширение спектра инновационных технологий и новых физических принципов, которые связаны с результатами фундаментальных работ и про-грессом в области элементной базы и технологий наноэлектроники, спинтроники и т.д., это вторая важная тенденция. Важно отметить, что мощным локомотивом развития в области АЗУ (и не только!) яв-ляются существенные изменения направлений развития информационных технологий в сторону облачных вычислений, машинного обучения, виртуальной реальности, автоном-ных систем, персональной медицины и т.д. [26]. Это третья тенденция. Четвертая тенденция заключается в том, что разработчики ИНС АЗУ имеют сейчас реальную возможность решать на основе первых двух тенденций следующие задачи: − использовать для ИНС АЗУ инновационную элементную базу: мемристорную [20-22], на основе углеродных материалов (графене, нанотрубках и т.д.) [18-19] и др., рис.2. При этом уже существуют разработки ИНС АЗУ, в которых удается эффективно комби-нировать как инновационные технологии, так и масштабированную технологию КМОП. Подробный сравнительный анализ инновационной элементной базы и технологий можно найти в [14, 15, 24]. Отдельные инновационные технологии рассматриваются в работах [16, 17]; − эффективно снижать энергопотребление в режиме выборки по содержимому. Ведь именно параллельность выполнения операции поиска нужной информации по всему мас-сиву элементов памяти является серьезной проблемой энергопотребления для ИМС АЗУ; − повышать быстродействие параллельного поиска при приемлемых уровнях потреб-ления мощности; − разрабатывать и использовать новые архитектуры и повышать интеллектуальность ИНС АЗУ, что не только повышает эффективность применения в традиционных областях (например, при построении кэш-памяти процессоров и для продвижения пакетов в аппа-ратуре высокоскоростных сетей [27-31]), но и существенно расширяет область использо-вания в сторону современных цифровых систем. Например, для нейроморфной ассоциа-тивной памяти [20-23], для различных мобильных и имплантируемых систем, гаджетов [32-35], для аппаратной реализации транзакционной памяти [36-38] и обработки «боль-ших данных» [39-42], для реконфигурируемых и приближенных вычислений [43-45] и т.д. Присоединённое изображение  -------------------- |

| VAL |

Дата 4.10.2019 09:55

|

Offline Мэтр, проФАН любви... proFAN of love      Профиль Группа: Администраторы Сообщений: 38172 Пользователь №: 1 Регистрация: 6.03.2004 |

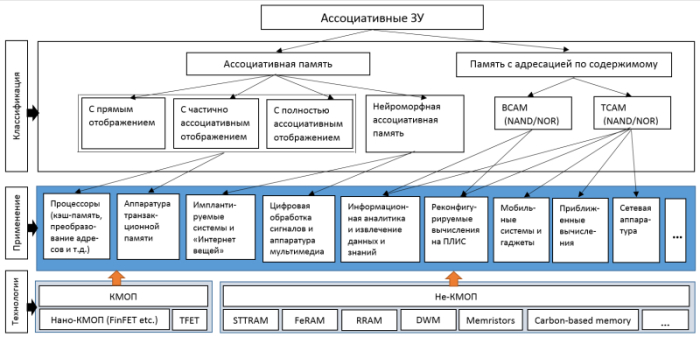

КЛАССИФИКАЦИЯ И ПРИМЕНЕНИЕ ИМС/ИНС АЗУ

Традиционная классификация АЗУ и ИМС/ ассоциативной памяти обычно ограничи-вается следующими признаками: вид поиска, способы опроса, выборки при множествен-ных совпадениях, способы записи информации [5, 6-10]. Однако для того, чтобы детально разобраться в состоянии дел в области ИНС АЗУ этой классификации явно недостаточно, поскольку она не отражает многие архитектурные, элементные и функциональные осо-бенности таких ИНС и возможности их применения и реализации. Память с выборкой по содержимому можно условно разделить на две основные формы: ассоциативную память (АП или AM – Associative Memory) и память с адресацией по содержимому (ПАС или CAM – Content Addressable Memory) [14]. Каждая из этих форм характеризуется признаком ассоциативности, но функционально эта ассоциатив-ность (при совпадении входных данных с хранимыми возвращается адрес нахождения искомых данных, либо − нуль при отсутствии совпадения/промахе) имеет различия. Для АМ характерно то, что область нахождения искомых данных ограничена со-держимым входных данных, который определяет соответствующий блок кэша и/или ос-новной памяти. К такой ассоциативной памяти относят (рис.2): - кэш-память прямого, частично-ассоциативного или множественно-ассоциативного и полного ассоциативного отображения основной памяти; - нейроморфная ассоциативная память, реализуемая на основе нейронных сетей. Особен-ность такой памяти в том, что ассоциативная выборка происходит в условиях «шума» или неполноты входных данных/признаков. Для ПАС подобное ограничение не принципиально – искомые данные могут нахо-дится в любом месте. При параллельном поиске в ПАС возможна реализация (рис.2): - полного совпадения входного совпадения/попадания (hit) исходного клю-ча/признака/паттерна с искомым или несовпадения/промаха (miss) в ПАС бинарного типа (ВСАМ - binary CAM); - частичного совпадения в ПАС троичного (или тернарного [1]) типа (TCAM – Ternary CAM), когда для поиска допускается использование признака/паттерна с маскированием отдельных бит или байт. Возможные варианты организации ПА и ПАС изображены в сводной классифика-ции на рис.2. Области применения представлены с учетом преимущественного использо-вания в виде и на основе ИМС/ИНС в табл.1. Присоединённое изображение  -------------------- |

| VAL |

Дата 4.10.2019 09:56

|

Offline Мэтр, проФАН любви... proFAN of love      Профиль Группа: Администраторы Сообщений: 38172 Пользователь №: 1 Регистрация: 6.03.2004 |

«УМНЫЕ» АССОЦИАТИВНЫЕ ИМС/ИНС АЗУ

Исходно наличие ассоциативности позволяет отнести ИМС/ИНС памяти к «умно-му» типу ЗУ [2, 3]. С другой стороны, если рассматривать архитектуру типовых ИНС/ИМС АЗУ [10, 46], то она в своем совершенствовании в сторону повышения интел-лектуальности во многом повторяет развитие типовой архитектуры ИМС/ИНС ОЗУ к ар-хитектуре PIM (processor-in-memory – процессоры-в-памяти). Анализ публикаций в области ИМС/ИНС АЗУ показывает, что появились идеи по разработке интегральных схем с дополнительными сервисными возможностями. Некото-рые примеры приведены в табл. 2. Следует отметить, что освещение архитектурных осо-бенностей «умных» ИНС АЗУ с дополнительными сервисными и процессорными функ-циональными возможностями требует специального обзора. -------------------- |

| VAL |

Дата 4.10.2019 09:56

|

Offline Мэтр, проФАН любви... proFAN of love      Профиль Группа: Администраторы Сообщений: 38172 Пользователь №: 1 Регистрация: 6.03.2004 |

ЗАКЛЮЧЕНИЕ

В настоящее время за рубежом широким фронтом ведутся исследования и разраба-тываются интегральные схемы АЗУ высокой степени интеграции, которые предназначе-ны для быстрого поиска хранимой информации и ее обработки по содержимому. Фунда-ментом для разработок служат новая наноэлектронная элементная база и технологии. В частности, инновационные технологии энергонезависимой памяти и элементной базы на мемристоров, углеродных нанотрубок и т.д. Степень интеграции существенно ИНС возросла. Прогнозируется ее увеличение до уровня 1010 элементов/см2. Таким образом, ИНС АЗУ являются весьма привлекательными для эффективного использования в быстро расширяющимся спектре применений: от ти-пового использования в аппаратуре быстродействующих сетей до построения нейро-морфной ассоциативной памяти и обработки «больших» данных. В будущем следует ожидать новых архитектурных решений и массового промышленного производства и применения «умных» ИНС АЗУ с дополнительными процессорными и сервисными воз-можностями. -------------------- |

| VAL |

Дата 4.10.2019 09:57

|

Offline Мэтр, проФАН любви... proFAN of love      Профиль Группа: Администраторы Сообщений: 38172 Пользователь №: 1 Регистрация: 6.03.2004 |

ЛИТЕРАТУРА

1. Лапшинский В.А. На пути к «умной» и «разумной» памяти: базовые кристаллы памя-ти и процессорно-ориентированная организация «умной» памяти // Датчики и систе-мы. − 2015. ‒ №1. ‒ С. 81-86. [Basic crystals and CPU-oriented organization “smart” memory // Sensors & Systems. ‒ 2015. ‒ № 1. ‒ P. 81‒86. (In Russian)] 2. Лапшинский В.А. На пути к интеллектуальным микросхемам памяти // Датчики и си-стемы. − 2016. ‒ №4. ‒ С. 81-86. [In the fair way to the smart and intelligent memory chips // Sensors & Systems. ‒ 2015. ‒ № 1. ‒ P. 77‒83 (In Russian)] 3. Lapshinsky V.A. Emerging Architectures for Processor-in-Memory Chips: Taxonomy and Im-plementation // RUDH Journal of Engineering Researches. – 2016. – N 14. – PP. 35−40. 4. Hanlon A. G. Content-addressable Memory and Associative Memory Systems // IEEE Trans-action on Electronic Computers. ‒ 1966. ‒ VOL. ES-15. ‒ NO 4. ‒ PP. 509−521. 5. Schultz K.J., Gulak P.G. Architectures for large-capacity CAMs // The VLSI Journal INTE-GRATION. ‒ 1995. ‒ N 18. ‒ PP. 151−171. 6. Крайзмер Л.П., Бородаев Д.А., Гутенмахер Л.И. и др. Ассоциативные запоминающие устройства. ‒ Ленинградское отд.: Энергия, 1967. ‒ 184 С. [Krizmer L.P., Borodaev D.A., Gutenmaher L.E. et al Content-Addressable Memory. ‒ L.: Energeia, 1967. ‒ 184 P. (книга) 7. Kobayashi K. A Study of the Functional Memory Type Parallel Processor // Kyoto Universi-ty. ‒ September 1998. ‒ 141 P. 8. Kohonen T. Content-Addressable Memory. ‒ New York, NY, USA. : Springer-Verlag, 1980. ‒ 384 P. 9. Орлов С.А., Цилькер Б.Я. Организация ЭВМ и систем: учебник для вузов. 2-е изд. – СПб.: Питер, 2011. – 680 с. [Orlov C.A., Tsilker B.Y. Organization of the computers and systems: textbook for universities. 2nd edition. – SPb.: Peter, 2011. – 240 p. (In Russian)]. (книга) 10. Pagiamtzis K., Sheikholeslami A. Content-addressable Memory (CAM) Circuits and Archi-tectures: A Tutorial and Survey // IEEE Journal of Solid-State Circuits. ‒ 2006, VOL. 41. ‒ N 3. ‒ PP. 712−727. 11. Aswathy K.S., Sheela K.G. Survey on Content-Addressable Memory and Sparse Clustered Network // International Journal of Advanced Computer Engineering and Communication Technology (IJACECT). ‒ 2014. ‒ Vol. 3. ‒ Iss. 3. ‒ PP. 15−24. 12. Memory - Customizable TCAMs and SRAMs. URL: http://www.analogbits.com/product_memory.htm. 13. Змеев Д.Н. и др. Тенденции развития архитектур ассоциативной памяти и ее примене-ние в параллельной потоковой вычислительной системе // МЭС-2016, Россия, Москва, ИППМ РАН, 2016. – С. 1−6. [Zmejev D.N. et al. Trends in development of content ad-dressable memory architectures and its application in the parallel dataflow computing system // MES-2016, Russia, Moscow, Institute for Design Problems in Microelectronics of RAS, 2016. – PP. 1−6 (In Russian)]. URL: http://www.mes-conference.ru/data/year2016/pdf/D157.pdf. 14. Karam R. et al. Emerging Trends in design and Application of Memory-Based Computing and Content-Addressable Memory // Proceeding of the IEEE. ‒ 2015. ‒ PP. 1311-1330. 15. Chen A. Beyond-CMOS Technology Roadmap // The ConFab, May 19-22, 2015. URL: http://electroiq.com/wp-content/uploads/20...resentation.pdf. 16. Jeloka S., Akesh N. B., Sylvester D, Blaauw D. A 28 nm Configurable Memory (TCAM/BCAM/SRAM) Using Push-Rule 6T Bit Cell Enabling Logic-in-Memory // IEEE J. of SSC. ‒ 2016. ‒ VOL. 51. ‒ NO 4. ‒ PP. 1009−1022. 17. Mittal S. A survey of Techniques for Architecting Processor Components using Domain Wall Memory // ACM J. on Emerging Technologies in Computing Systems (JETC) − Special Issue on Nanoelectronic Circuit and System Design Methods for the Mobile Computing Era and Regular Papers, 2017. – Vol. 13. – Iss. 2. – Article No. 29. Doi: 10.1145/2994550. 18. Khasanvis S., Rahman M., Moritz C.A. Heterogeneous Graphene-CMOS Ternary Content Addressable Memory // Journal of Parallel and Distributed Computing, 2014. – Vol. 74. – Iss. 6. − PP. 2497−2503. 19. Hellkamp D., Nepal K. Metallic tube-tolerant ternary dynamic content-addressable memory based on carbon nanotube transistors // Micro & Nan Letters, 2015. No. 10(4). − PP. 209−212. DOI: 10.1049/mnl.2014.0582. 20. Галушкин А.И. На пути к нейрокомпьютерам с использованием мемристоров // Наци-ональный Суперкомпьютерный Форум (НСКФ-2013), Россия, Переславль-Залесский, ИПС имени А.К. Айламазяна РАН, 26-29 ноября 2013 года, 2013. – С. 1−47. [Galushkin A. I. On the way to the Neurocomputers using memristors // National Supercomputing Forum (NSCF-2013), Russia, Pereslavl-Zalesskiy, IPS named A. K. Aylamazyan, Russian Academy of Sciences, 26-29 Nov 2013, 2013. – PP. 1−47]. 21. Rahimi A. et al. Energy-Efficient GPGPU Architectures via Collaborative Compilation and Memristive Memory-Based Computing // DAC’14, June 01 - 05 2014, San Francisco, CA, USA, 2014. – PP. 1−6. URL: http://mesl.ucsd.edu/site/pubs/DAC14_Abbas.pdf. 22. Schuman C.D. et al. A Survey of Neuromorphic Computing and Neural Networks in Hard-ware // U.S. Department of Energy, 2017. − PP. 1−88. URL: https://arxiv.org/pdf/1705.06963.pdf. 23. Trivedi A. R., Datta S. and Mukhopadhyay S. Application of silicon-germanium source tun-nel-FET to enable ultralow power cellular neural network-based associative memory // IEEE Trans. Electron Devices, 2014. ‒ VOL. 61. ‒ NO. 11. ‒ PP. 3707–3715. 24. Chen A. A. review of emerging non-volatile memory (NVM) technologies and applications // Solid-State Electronics, 2016. ‒ Vol. 125. ‒ PР. 25–38. 25. Emerging Non-Volatile Memory. Patent Landscape. ‒ 2014 February. URL: http://www.knowmade.com/Survey/Sample-eNVM...dscape-2014.pdf. 26. Ceze L., Hill M.D., Wenisch T.E. Arch2030: A Vision of Computer Architecture Research over the Next 15 Years // Computer Research Association. − January 2017. − Vol. 29. − No. 1. – PP. 1−12. 27. Banerjee-Mishra T. TCAM-based Low Power Routers and Pocket Classifiers // Ph.D. disser-tation // University of Florida. – 2012. – PP. 1−234. 28. Taylor D.E. Survey and Taxonomy of Packet Classification Techniques // Report Number: WUCSE-2004-24. – 2004. PP. 1−45. 29. Agrawal B., Sherwood T. Modeling TCAM Power for Next Generation Network Devices // In Proceedings of IEEE International Symposium on Performance Analysis of Systems and Software (ISPASS-2006). – 2006. – PP. 1−10. 30. Mathan K., Ravichandran T. Data Intelligent Low Power High Performance TCAM for IP-Address Lookup Table // Circuits and Systems. ‒ 2016. ‒ VOL. 07. ‒ NO 11. ‒ PP. 3734−3745. 31. Cronin B. Hardware Acceleration of Network Intrusion Detection and Prevention // Ph. D. dissertation, Dublin City University, School of Electronic Eng. – 2014. – PP. 1−197. 32. Mohammad K., Tumar I. Optimized large-capacity content addressable memory (CAM) for mobile devices // Proc. SPIE 9411, Mobile Devices and Multimedia: Enabling Technologies, Algorithms, and Applications 2015, 94110E (11 March 2015); DOI: 10.1117/12.2084505 33. Constandinou T. Neural Interfaces & Microsystems: from State-of-the -Art to the Next Gen-eration // CNRS/INSIS Workshop “Bioelectronics and Bioelectromagnetics”, 2016. – PP. 1−28. URL: www.cnrs.fr/insis/recherche/docs-evenements/WorkshopINSIS_ TConstandi-nou.pdf. 34. Narasimhan S. Ultralow-power and robust implantable neural interfaces: An algorithm-architecture-circuit co-design approach, Ph.D. dissertation // Dept. Electr. Eng. Comput. Sci., Case Western Reserve Univ., Cleveland, OH, USA, 2012. – PP. 1−160. 35. Narasimhan S.M., Bhunia S. Ultralow-Power and Robust Embedded Memory for Bi-oimplantable Microsystems // 26th International Conference on VLSI Design and the 12th International Conference on Embedded Systems, 2013. – PP. 1−6. 36. Kulkarni S. et al. Taxonomy for Transactional Memory Systems // Int. J. of Computer Science and Information Technologies. ‒ 2011. ‒ VOL. 27. ‒ NO 2 (2). ‒ PP. 766−775. 37. Leis V., Kemper A., Neumann T. Exploiting Hardware Transactional Memory in Main-Memory Databases // SIGMOD 2014. ‒ 2014. ‒ PP. 1−13. URL: http://db.in.tum.de/~leis/papers/HTM.pdf. 38. Levandoski J. et al. High Performance Transactions in Deuteronomy // 7th Biennial Confer-ence on Innovative Data Systems Research (CIDR’15) January 4-7, 2015, Asilomar, Cali-fornia, USA. ‒ 2016. ‒ PP. 1−12. URL: https://www.microsoft.com/en-us/research/wp...DR2015-full.pdf. 39. Guo Q., Guo X., Bai Y. and Ipek E. A resistive TCAM accelerator for data-intensive compu-ting // in Proc. 44th Annu. IEEE/ACM Int. Symp. Microarchitecture, 2011. − pp. 339–350. URL: http://www.ece.rochester.edu/~xiguo/micro11.pdf. 40. Gorodetsky V., Tushkanova O. Associative classification: analytical overview. Part 1 // SPIIRAS Proceedings. − 2015. − Issue 1(38). – PP. 183−2003. 41. Zhang H. et al. In-Memory Big Data Management and Processing: A Survey // IEEE Trans-actions on Knowledge and Data Engineering. ‒ 2015. ‒ VOL. 27. ‒ NO 7. ‒ PP. 1920−1948. 42. Murthy P. Big Data Taxonomy // BIG DATA WORKING GROUP. − 2014. ‒ PP. 1−33. URL: https://downloads.cloudsecurityalliance.org...ta_Taxonomy.pdf. 43. Bremler-Barr A. et al. Ultra-Fast Similarity Search Using Ternary Content Addressable Memory // DaMoN 2015, June 1, Melbourne, VIC, Australia. – 2015. – PP. 1−10. URL: http://www.deepness-lab.org/pubs/damon15_knn.pdf. 44. Imani M. IoT Hardware: From NVM to Approximate Computing // University of California, San Diego. ‒ Winter 2016. URL: https://cseweb.ucsd.edu/classes/wi16/cse291...oT_Hardware.pdf. 45. Ma Y. et al. A 600-µW ultra-low-power associative processor for image pattern recognition employing magnetic tunnel junction-based nonvolatile memories with autonomic intelligent power-gating scheme // Japanese Journal of Applied Physics. ‒ 2016. ‒ VOL. 55. ‒ NO 4S. ‒ PP. 46. Loh H. G. et al. A Processing-in-Memory Taxonomy and a Case for Studying Fixed-Function PIM // 1st Workshop on Near-Data Processing (WoNDP-2013), USA, Davis, California. URL: http://www.cs.utah.edu/wondp/wondp2013-paper2-final.pdf. 47. Yang H.-Y. et al. Testing methods for quaternary content addressable memory using charge-sharing sensing scheme // Test Conference (ITC), 6-8 Oct. 2015. DOI: 10.1109/TEST.2015. 7342409. 48. Built-in test method for content addressable memories // Patent US 6286116 B1, 2001. 49. Content addressable memory (CAM) devices that support background BIST and BISR oper-ations and methods of operating same // Patent US 7304875 B1, 2007. 50. Systems for built-in-self-test for content addressable memories and methods of operating the same // Patent US 7130230 B2, 2006. 51. Built-in self test for content addressable memory (патент US 6550034 B1) // Patent US 6550034 B1, 2003. 52. Lai C.-K., Huang Y.-J., Li J.-F. A Self-Repair Technique for Content Addressable Memories with Address-Input-Free Writing Function // J. of Information Science and Engineering, 2013. – NO. 29. – PP. 493−507. 53. Pontarelli S. et al. Error detection in Ternary CAMs using Bloom Filters // Proc. of Conf. “Design, Automation & Test in Europe Conference & Exhibition” Grenoble, France, March 18-22, 2013. – PP. 1−6 54. Dhiliban S., Saraswathi S. Realization of Low Power and High Speeds S-TCAM with A Check bit // The Int. J. of Engineering And Science, 2015. – No. 3. – PP. 117−123. 55. Shafiq M. Z. et al. TCAMChecker: A Software Approach to the Error Detection and Correc-tion of TCAM-Based Networking Systems // Springer J. Netw. Syst. Manage, 2013 PP. 335–352. 56. Bremler-Barr A. et al. PEDS: A Parallel Error Detection Scheme for TCAM Devices // EEE/ACM TRANSACTIONS ON NETWORKING, 2010. – VOL. 18. – NO. 5. − PP. 1665−1675. 57. Lu S.-K., Lin G.-Q., Kuo S.-Y. Yield Enhancement Techniques for Content-Addressable Memories // The 38th Annual IEEE/IFIP International Conference on Dependable Systems and Networks, 2008. – PP. 1−3. 58. Imani M., Rosing T. CAP: Configurable Resistive Associative Processor for Near-Data Com-puting // 1st Workshop on Near-Data Processing (WoNDP-2013), USA, Davis, California. URL: http://moimani.weebly.com/uploads/2/3/8/6/...maniisqed17.pdf. -------------------- |

| VAL |

Дата 22.01.2022 17:24

|

Offline Мэтр, проФАН любви... proFAN of love      Профиль Группа: Администраторы Сообщений: 38172 Пользователь №: 1 Регистрация: 6.03.2004 |

:doh:

-------------------- |

1 Пользователей читают эту тему (1 Гостей и 0 Скрытых Пользователей)

0 Пользователей:

|

|

Powered by Invision Power Board(U) v1.3 Final © 2003 IPS, Inc.

Установка, модификация и поддержка:

Barsum | 1px Design Group & Xac | OппаRU форум

Установка, модификация и поддержка:

Barsum | 1px Design Group & Xac | OппаRU форум