|

|

|

|

Помощь Помощь

Поиск Поиск

Участники Участники

Календарь Календарь

Новости Новости

|

Учебные Материалы Учебные Материалы

ВАЛтест ВАЛтест

Фотогалерея Фотогалерея

|

Правила форума Правила форума

Виртуальные тренажеры Виртуальные тренажеры

Мемуары Мемуары

|

| Здравствуйте Гость ( Вход | Регистрация ) | Выслать повторно письмо для активации |

|

| Alexashka |

Дата 9.10.2009 10:21

|

Offline Первокурсник  Профиль Группа: Выпускники Сообщений: 47 Пользователь №: 8125 Регистрация: 18.09.2009 |

Проектирование СБИС

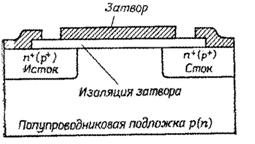

1. Направление проектирования СБИС На данном этапе развития СБИС, стоимость электронных схем входящих в состав СБИС, снижается с уменьшением размеров её элементов. По этой причине усилия разработчиков концентрируются на совершенствовании методов микротехнологии. Весь процесс проектирования можно разделить на электрическое и физическое проектирование. К электрическому проектированию относятся функциональное проектирование СБИС, логическое проектирование, проектирование схем и частично полупроводниковых приборов. Физическое проектирование решает задачи, относящиеся к микроструктуре СБИС, размещения полупроводниковых приборов, трассировки и т.п. 2. Базовые схемы На первый взгляд кристалл БИС представляется весьма сложной системой схем, в которой очень большое количество транзисторов, резисторов, конденсаторов и т.п.соединенных между собой методом послойного монтажа. По факту же внутри кристалла, как правило, содержится регулярная совокупность сравнительно простых базовых схем. Активные элементы применяемые в БИС. Подразделяются на полевые биполярные транзисторы. Широкое применение в БИС получили полевые транзисторы с изолированным затвором. Рис.1. Рис.1 Структура полевого МОП - транзистора Присоединённое изображение  -------------------- Только Спартак, только победа!

|

| Alexashka |

Дата 9.10.2009 10:29

|

Offline Первокурсник  Профиль Группа: Выпускники Сообщений: 47 Пользователь №: 8125 Регистрация: 18.09.2009 |

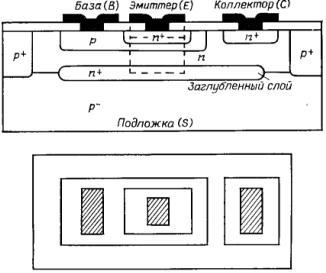

Но и биполярные транзисторы так же находят применение в БИС. Рис.2

Рис.2 Разрез и вид сверху планарного биполярного транзистора Присоединённое изображение  -------------------- Только Спартак, только победа!

|

| Alexashka |

Дата 9.10.2009 10:30

|

Offline Первокурсник  Профиль Группа: Выпускники Сообщений: 47 Пользователь №: 8125 Регистрация: 18.09.2009 |

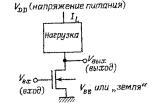

Использование базовых логических схем на МОП - структурах, подразумевает наличие в схемах МОП – инверторов, управляющих вентилей инвертирующих вентилей. Рис.3

Рис.3 Базовая схема основного МОП - инвертора Присоединённое изображение  -------------------- Только Спартак, только победа!

|

| Alexashka |

Дата 9.10.2009 10:33

|

Offline Первокурсник  Профиль Группа: Выпускники Сообщений: 47 Пользователь №: 8125 Регистрация: 18.09.2009 |

Инвертор- это электрическая схема, реализующая операцию логического отрицания, так же инвертор обладает функцией усиления слабых электрических сигналов и их воспроизведения.

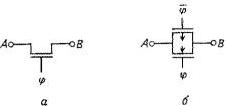

Управляющие вентили в функциональном плане одинаковые они размыкают или замыкают цепь передачи сигнала.Рис.4 Рис.4 Вентили передачи. а – на МОП – транзисторах, б – на КМОП – транзисторах. Присоединённое изображение  -------------------- Только Спартак, только победа!

|

| Alexashka |

Дата 9.10.2009 10:50

|

Offline Первокурсник  Профиль Группа: Выпускники Сообщений: 47 Пользователь №: 8125 Регистрация: 18.09.2009 |

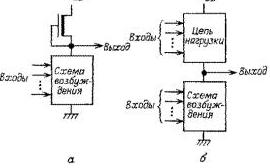

Устройства, в которых цепи возбуждения и цепи нагрузки объединены в одной инвертирующей схеме, называется инвертирующим вентилем. Рис.5

Рис.5 Структура вентилей – инверторов. б – на КМОП транзисторах,а – на транзисторах работающих в режимах обогащения/обеднения. Присоединённое изображение  -------------------- Только Спартак, только победа!

|

| Alexashka |

Дата 9.10.2009 10:53

|

Offline Первокурсник  Профиль Группа: Выпускники Сообщений: 47 Пользователь №: 8125 Регистрация: 18.09.2009 |

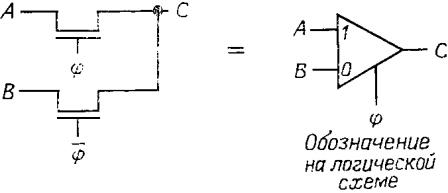

Соединив некоторое количество вентилей передачи, можно реализовать, вентили с определенными логическими функциями.

Схема мультиплексора/ демультиплексора. Рис.6 Рис.6 Схема 2-1 мультиплексора/демультиплексора. Это сообщение отредактировал Alexashka - 14.10.2009 08:58 Присоединённое изображение  -------------------- Только Спартак, только победа!

|

| Alexashka |

Дата 9.10.2009 11:01

|

Offline Первокурсник  Профиль Группа: Выпускники Сообщений: 47 Пользователь №: 8125 Регистрация: 18.09.2009 |

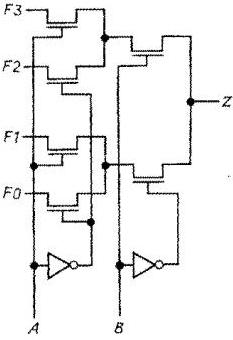

Дальнейшее объединение таких базовых схем приведёт к образованию схемы генератора функций. Рис.7

Рис.7 Схема генератора функций Это сообщение отредактировал Alexashka - 14.10.2009 08:58 Присоединённое изображение  -------------------- Только Спартак, только победа!

|

| Alexashka |

Дата 9.10.2009 11:31

|

Offline Первокурсник  Профиль Группа: Выпускники Сообщений: 47 Пользователь №: 8125 Регистрация: 18.09.2009 |

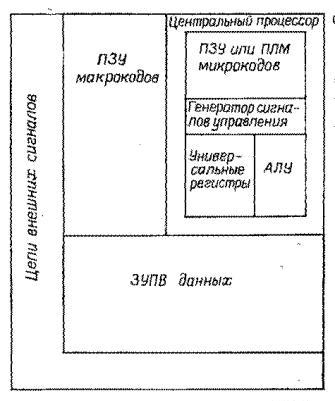

Комбинируя рассмотренные выше базисные схемы ,на основе МОП БИС представляется возможным реализовать устройства с самыми разнообразными функциями. На рисунке представлена

блок – схема ЭВМ выполненная в виде однокристальной БИС. Рис.8 Рис.8 Блок – схема ЭВМ выполненная в виде однокристальной БИС. Присоединённое изображение  -------------------- Только Спартак, только победа!

|

| Alexashka |

Дата 9.10.2009 11:33

|

Offline Первокурсник  Профиль Группа: Выпускники Сообщений: 47 Пользователь №: 8125 Регистрация: 18.09.2009 |

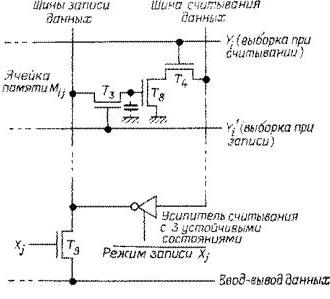

Запоминающее устройство на данной блок-схеме имеет вид. Рис.9

Рис.9 Схема динамического запоминающего устройства на трёх транзисторах Присоединённое изображение  -------------------- Только Спартак, только победа!

|

| Alexashka |

Дата 9.10.2009 11:34

|

Offline Первокурсник  Профиль Группа: Выпускники Сообщений: 47 Пользователь №: 8125 Регистрация: 18.09.2009 |

3. Моделирование электронных схем

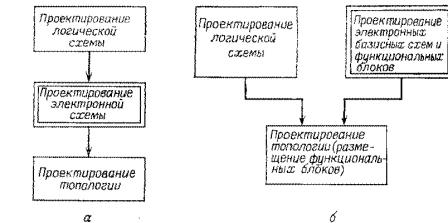

Целью проектирования электронных схем является определение структуры схемы и параметров её элементов, которые удовлетворяли бы требованиям предъявленным к схеме. Процесс проектирования показан на схемах. Рис.10 Рис.10 Последовательности проектирования СБИС а) Проектирование от верхнего уровня к нижнему. В этом случае все логические схемы трансформируются до уровня электронных и на этом этапе производится оценка результатов проектирования с использованием моделирующей программы. При отсутствии ошибок переходят к проектированию технологии БИС. б) Проектирование от нижнего уровня к верхнему. Согласно этому метод, исходя из базовых схем и функциональных блоков, производят проектирование БИС на уровне электронных схем и топологии внутри каждого функционального блока, а затем, привлекая функциональную схему, переходят, отполученых результатов к уже спроектированным блокам, таким образом , основную роль при проектировании топологии здесь играют размещение блоков и трассировки между ними. Присоединённое изображение  -------------------- Только Спартак, только победа!

|

| Alexashka |

Дата 9.10.2009 11:38

|

Offline Первокурсник  Профиль Группа: Выпускники Сообщений: 47 Пользователь №: 8125 Регистрация: 18.09.2009 |

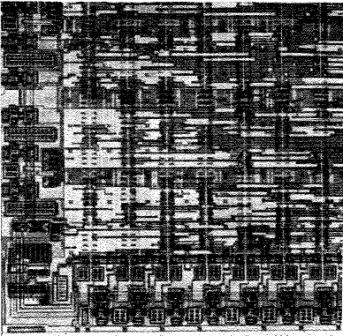

4.Проектирование топологии

При проектирование цифровых логических схем искомую схему в общем случае получают, комбинируя элементы (вентили, триггеры, ПЗУ и т.п.) Результатом проектирования на данном этапе представляет собой файл, в который вносится информация о логической схеме, о применяемых блоках характере соединения между собой. При разработке топологии в области прямоугольной формы размещают множество блоков и соединяют их электронными проводниками. Не забывая при этом о возможном влиянии проводников друг на друга и ближайших к ним блокам. Проектирование топологии требует гораздо больших экономических и временных затрат. Основное отличие от других стадий проектирования это то, что результаты проектирования с помощью автоматики в разы хуже чем, у ручного труда. Однако при ручном проектировании слишком большое число ошибок, поэтому выбирается диалоговый режим работы, при котором функции надлежащим образом разделены. . Рис.11 БИС типа вентильной матрицы на МОП – структурах. Присоединённое изображение  -------------------- Только Спартак, только победа!

|

| VAL |

Дата 9.10.2009 12:02

|

Offline Мэтр, проФАН любви... proFAN of love      Профиль Группа: Администраторы Сообщений: 38172 Пользователь №: 1 Регистрация: 6.03.2004 |

Alexashka

Все получилось! Спасибо! :) -------------------- |

| VAL |

Дата 18.10.2011 19:21

|

Offline Мэтр, проФАН любви... proFAN of love      Профиль Группа: Администраторы Сообщений: 38172 Пользователь №: 1 Регистрация: 6.03.2004 |

:doh:

-------------------- |

1 Пользователей читают эту тему (1 Гостей и 0 Скрытых Пользователей)

0 Пользователей:

|

|

Powered by Invision Power Board(U) v1.3 Final © 2003 IPS, Inc.

Установка, модификация и поддержка:

Barsum | 1px Design Group & Xac | OппаRU форум

Установка, модификация и поддержка:

Barsum | 1px Design Group & Xac | OппаRU форум